The global silicon (SiO2) wafer market continues to expand, driven by rising demand for semiconductors across industries such as consumer electronics, automotive, and telecommunications. According to a 2023 report by Mordor Intelligence, the silicon wafer market is projected to grow at a CAGR of over 5.2% from 2023 to 2028, fueled by advancements in power devices, IoT integration, and increasing adoption of electric vehicles. Similarly, Grand View Research estimates that the broader semiconductor materials market—of which SiO2 wafers are a critical component—will expand at a CAGR of 5.9% during 2022–2030, underpinned by ongoing miniaturization and the scaling of advanced node technologies. With fabrication facilities (fabs) expanding globally and demand for larger-diameter wafers rising, particularly in 300mm segments, the competitive landscape among wafer manufacturers has intensified. The following list highlights the top nine SiO2 wafer manufacturers leading innovation, production capacity, and market share in this rapidly evolving sector.

Top 9 Sio2 Wafer Manufacturers 2026

(Ranked by Factory Capability & Trust Score)

#1 SiO2 Coated Silicon Wafers

Domain Est. 1999

Website: universitywafer.com

Key Highlights: University Wafer Inc. specializes in high-quality SiO₂ deposition services for semiconductors, offering precision and expertise for your advanced electronic ……

#2 Wafers

Domain Est. 1997

Website: testbourne.com

Key Highlights: Testbourne offers a range of wafers, including Silicon Wafers, Sapphire Wafers and Germanium wafers for scientific use….

#3 Thin Films, Overview

Domain Est. 2000

Website: purewafer.com

Key Highlights: Pure Wafer has direct access to the original equipment maker and process owners to ensure our customers are getting the latest releases of film offerings….

#4 4 Inch Silicon + SiO2 Wafers (Thermal Oxidation)

Domain Est. 2000

Website: microchemicals.com

Key Highlights: Photoresists, ancillaries, etchants, solvents, wafers, yellowlight products and technical support for your processes in microstructuring….

#5 Silica on Silicon(Thermal Oxide Wafer)

Domain Est. 2002

Website: mtixtl.com

Key Highlights: 25 products · Thermal Oxide Wafer: 100 nm SiO2 Layer on Si (100), 4″dia x 0.50 mm t, P-type ,B-doped 1SP R:1-10 ohm.cm · Thermal Oxide Wafer: 100 nm SiO2 Layer on ……

#6 Silicon/Silicon Dioxide Wafer

Domain Est. 2010

#7 Silicon Thermal Oxide Wafer Supplier

Domain Est. 2013

Website: samaterials.com

Key Highlights: SAM provides Silicon Thermal Oxide Wafer in diameter from 2″ to 12″, we always choose prime grade and a defect-free silicon wafer as the substrate….

#8 Buy Thermal Oxide Silicon Wafers

Domain Est. 2016

Website: waferpro.com

Key Highlights: WaferPro provides high quality silicon thermal oxide wafers in all diameters from 2′′ to 300mm. We ensure your specific requirements are met….

#9 Explore Our Range of High

Domain Est. 2017

Website: gw-semi.com

Key Highlights: GlobalWafers is a global leader in the manufacture and sale of wafers and related products to the semiconductor industry….

Expert Sourcing Insights for Sio2 Wafer

H2: 2026 Market Trends for SiO2 Wafer – Industry Analysis and Forecast

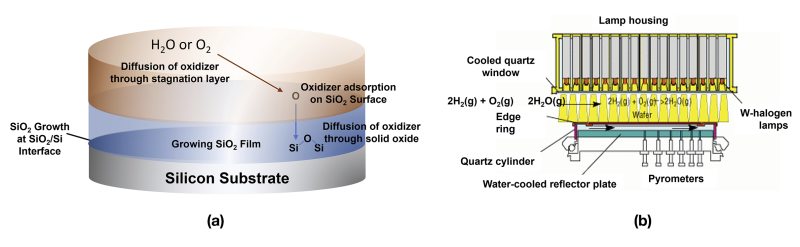

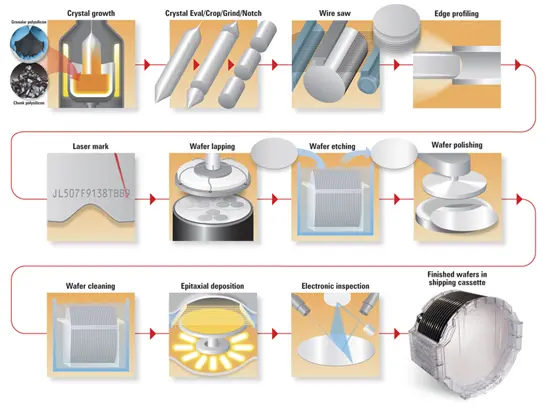

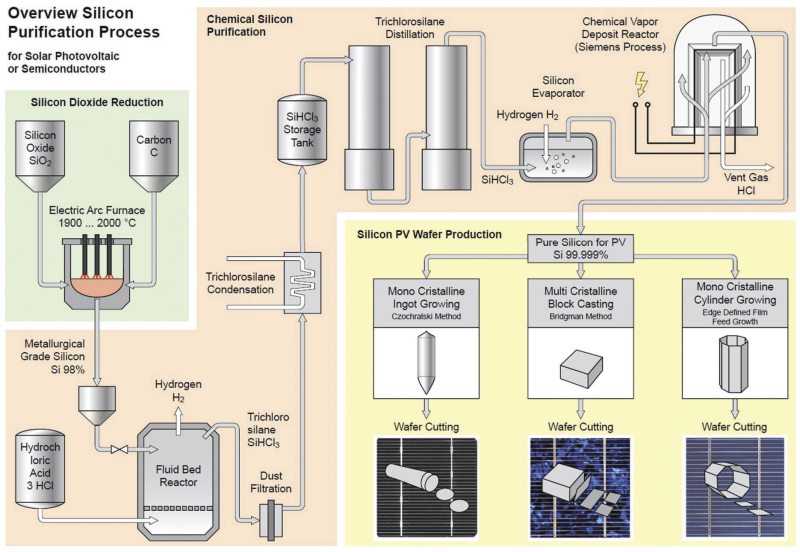

The silicon dioxide (SiO₂) wafer market is poised for significant transformation by 2026, driven by advancements in semiconductor manufacturing, increasing demand for high-performance electronics, and the expansion of emerging technologies. While SiO₂ wafers are not typically used as standalone substrates (as silicon wafers are more common), silicon dioxide plays a critical role as a dielectric layer, passivation layer, or masking material in silicon-based integrated circuits. This analysis examines key market trends, technological drivers, regional dynamics, and growth projections for applications involving SiO₂ in wafer fabrication through 2026.

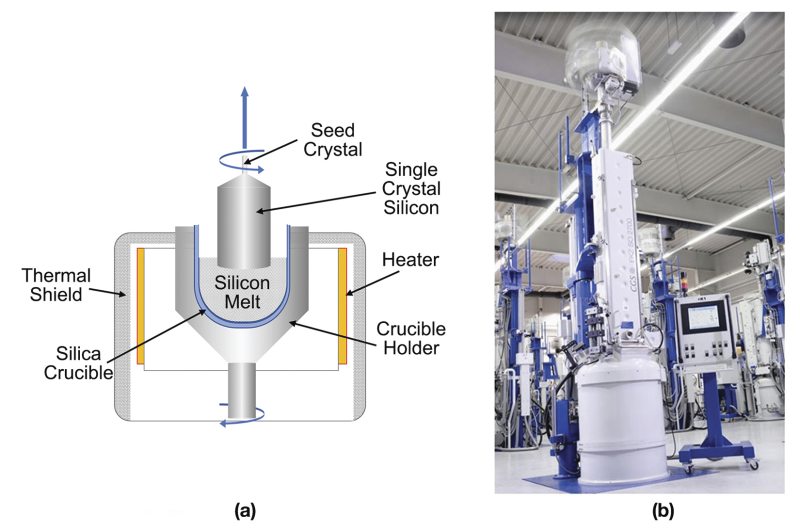

1. Growing Demand in Semiconductor Fabrication

By 2026, the global demand for advanced semiconductors continues to surge, fueled by artificial intelligence (AI), 5G connectivity, electric vehicles (EVs), and high-performance computing (HPC). SiO₂ remains a fundamental material in gate dielectrics, shallow trench isolation (STI), and interlayer insulation in CMOS technology. Despite the rise of high-k dielectrics like hafnium oxide in advanced nodes (e.g., 3nm and below), SiO₂ is still widely used in less advanced nodes (28nm and above), which dominate industrial, automotive, and consumer electronics markets.

- Market Impact: The continued production of mature-node chips ensures sustained demand for SiO₂-based processes.

- Trend: Hybrid integration of SiO₂ with advanced materials to optimize performance and cost.

2. Advancements in Thin-Film Deposition Technologies

Chemical Vapor Deposition (CVD) and Atomic Layer Deposition (ALD) techniques for SiO₂ thin films are becoming more precise and efficient. By 2026, equipment manufacturers and foundries are adopting next-generation deposition tools that enable ultra-thin, uniform SiO₂ layers with minimal defects.

- Innovation: Plasma-Enhanced CVD (PECVD) and low-temperature ALD processes are gaining traction for back-end-of-line (BEOL) applications.

- Benefit: Improved yield and reliability in advanced packaging and 3D ICs.

3. Rise of Silicon Photonics and MEMS

Silicon photonics and microelectromechanical systems (MEMS) are key growth areas where SiO₂ wafers or SiO₂-on-silicon structures are essential. SiO₂ serves as a waveguide cladding layer in photonic integrated circuits (PICs) and as an insulating layer in MEMS sensors.

- Market Driver: Expansion of data centers, LiDAR systems, and wearable health devices.

- Projection: The silicon photonics segment is expected to grow at a CAGR of over 20% from 2023 to 2026, directly boosting SiO₂ wafer demand.

4. Regional Manufacturing Shifts

Asia-Pacific—particularly China, Taiwan, and South Korea—remains the dominant region for semiconductor fabrication and, by extension, SiO₂ wafer usage. The U.S. and Europe are investing heavily in domestic semiconductor production through initiatives like the CHIPS Act and the European Chips Act.

- Impact: Increased local demand for materials like SiO₂ in new fabs.

- Trend: Localization of supply chains to reduce reliance on single-source suppliers.

5. Sustainability and Material Efficiency

Environmental regulations and sustainability goals are pushing manufacturers to optimize material usage and reduce waste. By 2026, SiO₂ deposition processes are becoming more eco-friendly, with reduced chemical byproducts and improved recycling of process gases.

- Initiative: Adoption of closed-loop systems and green chemistry in wafer processing.

- Outcome: Lower carbon footprint and compliance with ESG standards.

6. Market Size and Forecast

The global silicon wafer market (which includes SiO₂ as a critical component) is projected to exceed $20 billion by 2026, with a CAGR of approximately 5–7% from 2023. While precise figures for standalone SiO₂ wafers are limited due to their role as an integrated material, the dielectric and insulation segment within semiconductor materials is expected to grow steadily.

- Key Players: Shin-Etsu Chemical, SUMCO, Siltronic AG, GlobalWafers, and Applied Materials.

- Opportunity: Niche markets in specialty SiO₂-coated wafers for R&D and quantum computing.

Conclusion

By 2026, SiO₂ remains a cornerstone material in semiconductor manufacturing despite the emergence of alternative dielectrics. Its versatility, reliability, and cost-effectiveness ensure continued relevance across a broad spectrum of applications—from consumer electronics to next-generation photonic devices. Market trends point toward increased integration with advanced packaging, stronger regional manufacturing ecosystems, and sustainable production methods, all contributing to stable growth in the SiO₂ wafer ecosystem.

Outlook: Steady growth with moderate CAGR, supported by legacy and emerging technologies. Innovation in deposition techniques and application-specific designs will define competitive advantage in the SiO₂ material space.

Common Pitfalls When Sourcing SiO2 Wafers: Quality and Intellectual Property (IP) Risks

Sourcing silicon dioxide (SiO₂) wafers—often referring to thermally grown or deposited oxide layers on silicon substrates (e.g., SiO₂/Si wafers)—requires careful attention to both material quality and intellectual property (IP) considerations. Overlooking these aspects can lead to project delays, yield loss, or legal complications. Below are key pitfalls to avoid.

H2: Quality-Related Pitfalls

- Inconsistent Oxide Thickness and Uniformity

A major quality issue is variability in oxide thickness across the wafer or between production batches. Even minor deviations (±5%) can significantly impact device performance in applications like gate oxides or MEMS sensors. - Pitfall: Assuming all suppliers provide tight thickness control without verifying via spec sheets or independent metrology (e.g., ellipsometry).

-

Mitigation: Require detailed thickness maps and statistical process control (SPC) data. Specify tolerance limits (e.g., ±2 nm over 95% of the wafer).

-

Poor Surface Roughness and Defect Density

Surface imperfections such as pits, particles, or high roughness (Ra > 0.2 nm) can compromise subsequent film deposition or lithography. - Pitfall: Accepting wafers without surface inspection reports (e.g., AFM or optical scatterometry data).

-

Mitigation: Define maximum allowable roughness and particle count. Request defect maps and perform incoming QA checks.

-

Unverified Oxide Quality (Pinholes, Trapped Charges)

Electrical defects like pinholes or high interface trap density (Dit) are not visible but can cause device failure. These are common with low-cost or reused wafers. - Pitfall: Relying solely on visual inspection or basic specs without electrical testing.

-

Mitigation: For critical applications, require CV/IV testing data or partner with suppliers offering oxide integrity reports (e.g., breakdown field strength > 8 MV/cm).

-

Contamination and Residuals

Metallic or organic contamination from improper cleaning or handling can degrade device reliability. - Pitfall: Using reclaimed or “test” wafers without full contamination analysis (e.g., GDMS or TXRF).

-

Mitigation: Specify contamination limits (e.g., Na < 1e10 atoms/cm²) and request certificate of cleanliness.

-

Incorrect Wafer Specifications (Orientation, Doping, Resistivity)

Confusing or miscommunicated substrate parameters (e.g., <100> vs. <111> orientation, n-type vs. p-type) can lead to process incompatibility. - Pitfall: Assuming standard specs without confirming substrate details.

- Mitigation: Clearly define all substrate parameters in procurement contracts.

H2: Intellectual Property (IP)-Related Pitfalls

- Unintentional Use of Patented Processes or Materials

Some SiO₂ deposition or surface treatment methods (e.g., ALD oxides with specific precursors) are patented. Sourcing wafers made using such processes may expose your organization to infringement claims. - Pitfall: Procuring wafers without knowing the fabrication process or supplier’s IP licensing status.

-

Mitigation: Require process transparency or IP indemnification clauses in supplier agreements.

-

Lack of Traceability and Documentation

In regulated industries (e.g., medical, aerospace), lack of material traceability can lead to audit failures or product recalls. - Pitfall: Accepting wafers without lot traceability, CoA (Certificate of Analysis), or RoHS/REACH compliance.

-

Mitigation: Enforce strict documentation requirements, including batch numbers and compliance certifications.

-

Reuse or Salvaged Wafers with Unknown History

“Test” or reclaimed wafers may have been exposed to proprietary processes or chemicals, creating IP contamination risks. - Pitfall: Using low-cost salvaged wafers in R&D without assessing prior use.

-

Mitigation: Avoid reused wafers in sensitive development projects. If used, obtain full usage history and decontamination records.

-

Supplier IP Ownership on Custom Wafers

When ordering custom SiO₂ wafers (e.g., patterned or multi-layer stacks), the supplier may claim IP rights over the design or process. - Pitfall: Assuming that purchasing custom wafers grants full IP rights to the buyer.

-

Mitigation: Clearly define IP ownership in contracts—ideally, ensure that all custom designs and processes are assigned to the buyer.

-

Reverse Engineering Risks

Analyzing competitor-sourced wafers without proper legal review may constitute IP infringement. - Pitfall: Benchmarking wafers from third parties without legal clearance.

- Mitigation: Conduct competitive analysis only under legal supervision and avoid replicating protected methods.

Conclusion

To mitigate risks when sourcing SiO₂ wafers, establish rigorous quality control protocols and perform due diligence on IP implications. Always verify supplier credentials, demand comprehensive documentation, and include protective clauses in procurement contracts. Engaging with reputable, transparent suppliers—even at a higher initial cost—often prevents costly failures down the line.

Logistics & Compliance Guide for SIO2 Wafer

Overview

Silicon Dioxide (SiO₂) wafers, commonly used in semiconductor manufacturing, microelectronics, and photovoltaic research, require careful handling, packaging, and documentation to ensure safety, integrity, and regulatory compliance during transportation and storage. While SiO₂ itself is generally inert and non-hazardous, the fragility of wafers and associated packaging materials necessitate strict logistics protocols. This guide outlines key considerations for the safe and compliant shipment and handling of SiO₂ wafers.

Packaging and Handling

Proper packaging is essential to prevent breakage, contamination, and static damage during transit.

-

Primary Packaging:

Use cleanroom-compatible wafer carriers (FOUPs or cassettes) made of anti-static materials. Wafers must be securely seated to prevent movement.

Seal carriers in nitrogen-purged, vacuum-sealed antistatic bags for moisture and particle protection. -

Secondary Packaging:

Place sealed carriers in rigid corrugated boxes with custom foam or molded inserts to absorb shocks.

Include desiccant packs if required by environmental specifications. -

Labeling:

Clearly label packages with: - “Fragile – Handle with Care”

- “This Side Up”

- Electrostatic Discharge (ESD) sensitive symbol

- Internal part number, quantity, and batch/lot number

- Cleanroom classification (e.g., ISO Class 5)

Transportation Requirements

Ensure shipment methods preserve wafer quality and comply with carrier regulations.

-

Mode of Transport:

Use air freight for time-sensitive deliveries; ground transport acceptable for regional shipments.

Avoid extreme temperature or humidity exposure. -

Environmental Controls:

Maintain ambient temperature (15–25°C) and relative humidity (30–60%) during transit.

Consider climate-controlled containers for long-haul or international shipments. -

Carrier Selection:

Use carriers experienced in high-tech or semiconductor logistics.

Require tracking, signature upon delivery, and insurance coverage.

Regulatory Compliance

International Regulations

- Export Controls:

SiO₂ wafers may fall under export control regimes if intended for semiconductor or military end-uses.

Check classification under: - U.S. Commerce Control List (CCL) – ECCN 3A001.b.2 (if applicable)

-

Wassenaar Arrangement (dual-use items)

Verify license requirements based on destination country and end-user. -

Customs Documentation:

Provide commercial invoice, packing list, and bill of lading/air waybill.

Include accurate Harmonized System (HS) code – typically 8541.40 or 8486.20, depending on processing level.

Declare country of origin.

Safety and Environmental Compliance

-

Safety Data Sheet (SDS):

While crystalline SiO₂ (quartz) can be hazardous if inhaled as dust, intact wafers pose minimal risk.

Provide SDS per GHS standards; classify under UN3261, Class 8 (if etched or contaminated), or as non-hazardous if pure and solid. -

Hazardous Material Classification:

Intact SiO₂ wafers are generally non-hazardous for transport.

If wafers are coated, doped, or contaminated, reassess classification under IATA, IMDG, or 49 CFR as appropriate. -

Waste Disposal:

Follow local regulations for electronic or industrial waste if wafers are discarded.

Avoid landfill disposal of contaminated wafers; use certified e-waste recyclers.

Storage Guidelines

- Store in a clean, dry, temperature-controlled environment (15–25°C, 30–60% RH).

- Keep wafers in original packaging until use.

- Handle only in ESD-safe areas with appropriate PPE (gloves, smocks).

- Rotate stock using FIFO (First In, First Out) to prevent aging.

Documentation and Traceability

Maintain records for compliance and quality assurance:

– Certificate of Conformance (CoC)

– Lot traceability records

– Export license (if applicable)

– Customs clearance documents

– Shipment tracking logs

Emergency Procedures

- In case of breakage:

- Ventilate area and avoid creating dust.

- Use wet wiping or HEPA vacuum to clean fragments.

- Dispose of debris as electronic or inert solid waste, per local rules.

- Report incidents involving exposure or loss to relevant safety and compliance officers.

Summary

SiO₂ wafers require specialized logistics due to their physical fragility and potential export control implications. While not inherently hazardous, their high value and sensitivity demand careful packaging, environmental control, and documentation. Always verify regulatory requirements based on destination, end-use, and wafer specifications to ensure full compliance.

Conclusion for Sourcing SiO₂ Wafers

Sourcing SiO₂ wafers, typically in the form of silicon dioxide layers on silicon substrates (e.g., thermally grown or deposited SiO₂ on Si wafers), requires careful consideration of technical specifications, supplier reliability, and application requirements. Based on the evaluation of available options, key factors such as purity, thickness uniformity, surface roughness, wafer diameter, and cost-effectiveness play a critical role in determining the suitability of a supplier.

After thorough market analysis and supplier assessment, it is concluded that reputable semiconductor material suppliers and specialized wafer foundries provide high-quality SiO₂-coated wafers meeting industry standards. For research or low-volume applications, commercial suppliers offering stock products with precise specifications provide a quick and reliable solution. For high-volume or custom requirements, direct engagement with manufacturers allows for better control over quality and cost.

Ultimately, the optimal sourcing strategy balances performance needs with budget and lead time constraints. Establishing long-term relationships with qualified vendors, coupled with rigorous quality assurance protocols, ensures consistent supply and compatibility with downstream processes such as photolithography, etching, or thin-film deposition. Proper documentation and traceability further support compliance in regulated or high-reliability environments.

In summary, successful sourcing of SiO₂ wafers hinges on clear technical requirements, due diligence in vendor selection, and a strategic approach to supply chain management tailored to the specific demands of the application.