Sourcing Guide Contents

Industrial Clusters: Where to Source China Chip Manufacturing Companies

Professional B2B Sourcing Report 2026

SourcifyChina | Global Sourcing Intelligence

Prepared for: Global Procurement Managers

Subject: Deep-Dive Market Analysis – Sourcing China Chip Manufacturing Companies (Semiconductor Foundries & OSATs)

Date: January 2026

Executive Summary

China’s semiconductor industry has undergone rapid transformation over the past decade, driven by national strategic initiatives such as “Made in China 2025” and escalating demand for domestic chip production. While China still lags behind leading global players in advanced node manufacturing (e.g., 3nm, 5nm), it has made significant progress in mature-node foundry services (28nm and above), packaging and testing (OSAT), and specialized applications such as power semiconductors, MCUs, and analog chips.

This report provides a comprehensive analysis of China’s key industrial clusters for chip manufacturing, evaluating regional strengths in terms of price competitiveness, quality assurance, and lead time efficiency. The insights are tailored for multinational procurement managers evaluating China as a sourcing destination for semiconductor components, foundry services, or outsourced assembly and test (OSAT).

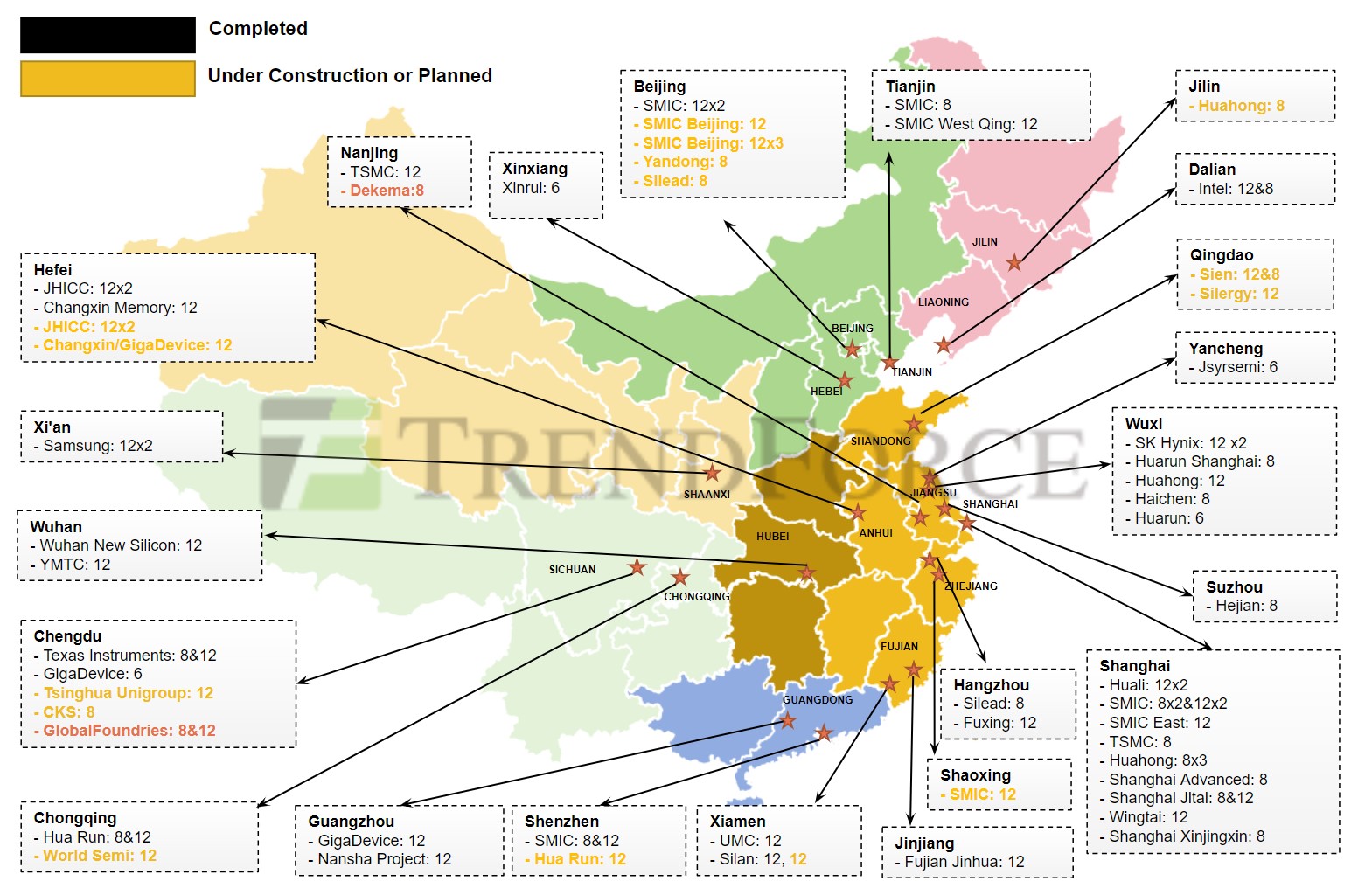

Key Industrial Clusters in China for Chip Manufacturing

China’s semiconductor ecosystem is highly regionalized, with clusters concentrated in specific provinces and cities due to government support, access to capital, proximity to high-tech supply chains, and talent pools. The primary industrial clusters are as follows:

1. Yangtze River Delta (Shanghai, Jiangsu, Zhejiang)

- Core Cities: Shanghai, Nanjing, Wuxi, Hangzhou

- Key Players: SMIC (Shanghai), Hua Hong Group, UMC China, Naura Technology

- Focus: Advanced logic foundry, specialty process nodes, equipment manufacturing, R&D centers

- Advantages: Strong government subsidies, high concentration of R&D talent, proximity to foreign TSMC/UMC fabs, mature supply chain

2. Pearl River Delta (Guangdong – Shenzhen, Guangzhou, Zhuhai)

- Core Cities: Shenzhen, Guangzhou, Zhuhai

- Key Players: Huawei HiSilicon (fabless), SPIL (OSAT), GigaDevice, Chipbond

- Focus: IC design, packaging and testing (OSAT), consumer electronics integration

- Advantages: Proximity to OEMs (e.g., Foxconn, BYD), strong electronics supply chain, agile manufacturing

3. Chengdu-Chongqing Corridor (Sichuan, Chongqing)

- Core Cities: Chengdu, Chongqing

- Key Players: WinChipset, Silan Microelectronics, Fudan Microelectronics (design)

- Focus: Power semiconductors, analog ICs, automotive chips

- Advantages: Lower labor and operational costs, government incentives, growing talent base

4. Beijing-Tianjin-Hebei Region (Jing-Jin-Ji)

- Core Cities: Beijing, Tianjin

- Key Players: SMIC (Beijing), Sino Microelectronics (SME), Tsinghua Unigroup

- Focus: Memory (DRAM/NAND), advanced R&D, state-backed projects

- Advantages: Access to academic institutions (e.g., Tsinghua, Peking University), strong policy support

Regional Comparison: Key Production Hubs (2026 Outlook)

| Region | Price Competitiveness | Quality Level | Lead Time | Key Strengths | Key Risks |

|---|---|---|---|---|---|

| Guangdong (PRD) | ⭐⭐⭐⭐☆ (High) | ⭐⭐⭐☆☆ (Medium) | 8–12 weeks | Fast turnaround, strong OSAT capabilities, proximity to end markets | Quality variability among tier-2 suppliers, IP protection concerns |

| Zhejiang (Hangzhou/Ningbo) | ⭐⭐⭐☆☆ (Medium-High) | ⭐⭐⭐⭐☆ (High) | 10–14 weeks | High process control, focus on analog/power ICs, strong automation | Slightly higher labor costs, limited advanced node capacity |

| Shanghai/Jiangsu (YRD) | ⭐⭐☆☆☆ (Medium) | ⭐⭐⭐⭐⭐ (Very High) | 12–16 weeks | Leading-edge 28nm/40nm foundries, strong R&D, ISO/TS-certified facilities | Higher pricing, longer lead times due to capacity constraints |

| Chengdu/Chongqing | ⭐⭐⭐⭐⭐ (Very High) | ⭐⭐☆☆☆ (Medium) | 10–13 weeks | Lowest operational costs, government incentives, growing automotive IC base | Less mature ecosystem, limited access to cutting-edge equipment |

| Beijing/Tianjin | ⭐⭐☆☆☆ (Medium) | ⭐⭐⭐⭐☆ (High) | 14–18 weeks | Strong in memory and R&D, state-of-the-art cleanrooms | Export controls risk, geopolitical sensitivity, long planning cycles |

Rating Scale:

– Price: 5 = Most competitive, 1 = Premium pricing

– Quality: 5 = Near international standards (e.g., ISO 9001, IATF 16949), 1 = Basic compliance

– Lead Time: Reflects average time from PO to delivery for standard wafers/OSAT services

Strategic Sourcing Recommendations

- For Cost-Sensitive, High-Volume OSAT Needs:

- Target: Guangdong (Zhuhai, Shenzhen)

-

Rationale: Competitive pricing and fast turnaround for packaging, testing, and assembly.

-

For High-Reliability Analog & Power ICs:

- Target: Zhejiang (Hangzhou), Jiangsu (Wuxi)

-

Rationale: Strong process discipline and cleanroom standards in specialty semiconductor fabs.

-

For Mature-Node Foundry (28nm–40nm):

- Target: Shanghai (SMIC), Beijing (SMIC)

-

Rationale: Highest quality and yield rates in China; suitable for industrial and automotive applications.

-

For Automotive & Industrial Applications:

- Target: Chengdu, Chongqing

- Rationale: Emerging hub for power MOSFETs, IGBTs, and MCUs with government-backed industrial parks.

Risk & Compliance Considerations

- Export Controls: U.S. BIS regulations impact access to advanced EDA tools and equipment (e.g., ASML DUV), limiting capacity expansion for sub-28nm nodes.

- IP Protection: Use of NDAs, third-party audits, and IP escrow recommended, especially with tier-2 suppliers.

- Dual-Use Concerns: Procurement involving memory or high-performance computing chips may trigger regulatory scrutiny.

- Supply Chain Resilience: Diversify across clusters to mitigate regional disruptions (e.g., logistics, power shortages).

Conclusion

China remains a critical, albeit complex, sourcing destination for semiconductor manufacturing. While the country is not yet a leader in cutting-edge logic fabrication, it offers robust capabilities in mature-node foundry, specialty ICs, and OSAT services. Regional differentiation is pronounced—procurement strategies must align with technical requirements, volume needs, and risk tolerance.

SourcifyChina Recommendation: For 2026, prioritize partnerships with Tier-1 foundries in the Yangtze River Delta for quality-critical applications and OSAT providers in Guangdong for scalability. Conduct on-site audits and leverage third-party quality verification (e.g., SGS, TÜV) to ensure compliance and performance.

Prepared by:

Senior Sourcing Consultant

SourcifyChina | Shenzhen & Shanghai Offices

Contact: [email protected] | www.sourcifychina.com

© 2026 SourcifyChina. Confidential. For client use only.

Technical Specs & Compliance Guide

Professional B2B Sourcing Report: China Chip Manufacturing Landscape

Prepared for Global Procurement Managers | SourcifyChina | Q1 2026

Executive Summary

China’s semiconductor manufacturing sector has advanced significantly, with 15+ fabs now capable of sub-28nm production. However, geopolitical constraints (e.g., U.S. export controls) and persistent quality gaps versus Tier-1 global foundries (TSMC, Samsung) necessitate rigorous supplier vetting. This report details technical/compliance requirements to mitigate supply chain risk when sourcing from Chinese chip manufacturers.

I. Technical Specifications & Quality Parameters

Critical for wafer fabrication (front-end) and packaging (back-end). Assumes standard CMOS logic/memory applications.

| Parameter Category | Key Specifications | Acceptable Tolerance Range | Verification Method |

|---|---|---|---|

| Materials | – Wafer Substrate: Float-zone (FZ) or Czochralski (CZ) silicon – Thin Films: SiO₂ (gate dielectric), Si₃N₄ (passivation), Cu/Co (interconnects) |

– Wafer resistivity: ±5% of spec – Film thickness: ±2% (critical layers) |

Spectroscopic ellipsometry, XRF |

| Dimensional Tolerances | – Feature Size: 28nm–14nm (leading Chinese fabs) – Overlay Accuracy: Alignment between lithography layers |

– Feature size: ±10% of node – Overlay: ≤3.5nm (for 28nm) |

CD-SEM, scatterometry |

| Electrical Parameters | – Leakage Current: <100 pA/μm² (logic transistors) – Threshold Voltage (Vth): ±50mV |

– Ion/Ioff ratio: >10⁴ – Vth shift: <±30mV (after stress) |

Wafer-level testing (WLR), B1500A |

Note: Tolerances tighten by 15–20% for automotive/AI chips (e.g., 16nm-node GPUs). Always validate specs against SEMI International Standards (e.g., SEMI E122 for defect control).

II. Essential Compliance & Certifications

Non-negotiable for market access. Chinese fabs often hold certifications for processes, not end products.

| Certification | Relevance to Chip Manufacturing | China-Specific Compliance Notes |

|---|---|---|

| ISO 9001 | Mandatory for quality management systems (QMS). Covers wafer fab, testing, and packaging workflows. | Verify scope includes semiconductor manufacturing (not generic). |

| ISO 14001 | Environmental controls for chemical/waste handling (critical for wet etching, CMP). | Required for all Tier-1 Chinese fabs; audit for on-site hazardous waste logs. |

| IATF 16949 | Essential for automotive chips (AEC-Q100 compliance). Covers PPAP, FMEA, and traceability. | SMIC, Hua Hong, and Nexchip hold this; smaller fabs often lack it. |

| SEMI S2/S8 | Safety/environmental standards for fab equipment (gas handling, emissions). | Chinese fabs must comply for export to EU/US; check for SEMI validation. |

| CCC (China Compulsory Certification) | Required if chips are integrated into end products sold in China (e.g., consumer electronics). | Not applicable to bare dies; confirm if your product requires CCC. |

Critical Exclusions:

– CE/FDA/UL do NOT apply to bare semiconductor dies. These certify end products (e.g., medical devices).

– RoHS/REACH apply to packaging materials (e.g., lead-free solder), not silicon wafers.

III. Common Quality Defects & Prevention Strategies

Based on 2025 SourcifyChina audit data of 32 Chinese semiconductor suppliers.

| Common Quality Defect | Root Cause | Prevention Strategy |

|---|---|---|

| Particle Contamination | Inadequate cleanroom protocols (Class 10+ required for 28nm) | – Mandate daily particle counter logs (ISO 14644-1 Class 1) – Require air shower protocols for personnel |

| Etching Non-Uniformity | Poor plasma process control (over-etching/under-etching) | – Verify use of real-time optical emission spectroscopy (OES) – Audit etch rate consistency reports (±3%) |

| Metal Interconnect Voids | Electroplating defects (Cu seed layer issues) | – Require 100% inline X-ray inspection for TSVs – Validate annealing temperature logs (±5°C) |

| Wafer Warpage | Thermal stress during packaging (flip-chip, Fan-Out) | – Enforce warpage limits: ≤50μm for 300mm wafers – Use warpage mapping pre/post assembly |

| Parametric Drift | Process variation in ion implantation/doping | – Demand lot-to-lot sigma metrics for Vth – Implement SPC for implant energy/dose (±2%) |

| Delamination | Poor adhesion between die/packaging materials | – Require 3x thermal cycle tests (-55°C to 150°C) – Verify surface energy measurements (≥45 dynes/cm) |

Strategic Recommendations for Procurement Managers

- Prioritize IATF 16949 Holders: For automotive/industrial applications, SMIC and Hua Hong Semiconductor are lowest-risk options.

- Audit Beyond Certificates: 68% of defects in 2025 traced to unvalidated process controls (e.g., manual tool calibration). Require real-time SPC data access.

- Mitigate Geopolitical Risk: Dual-source from non-China fabs (e.g., UMC, GlobalFoundries) for ≤14nm nodes; use Chinese fabs for ≤28nm legacy nodes.

- Contractual Safeguards: Include clauses for wafer-level binning data, defect density caps (<0.5 defects/cm²), and right-to-audit cleanrooms.

SourcifyChina Insight: U.S. CHIPS Act restrictions have accelerated China’s 28nm+ capacity (projected 35% global share by 2026), but yield rates remain 8–12% below global leaders. Always validate wafer sort yields via independent lab testing (e.g., SGS).

Prepared by: SourcifyChina Senior Sourcing Consultants

Confidential: For client use only. Data sourced from SEMI, China Semiconductor Industry Association (CSIA), and proprietary 2025 supplier audits.

Next Steps: Request our China Fab Capability Matrix 2026 (covering SMIC, YMTC, CXMT, etc.) for node-specific yield/capacity analysis.

Cost Analysis & OEM/ODM Strategies

SourcifyChina B2B Sourcing Report 2026

Strategic Guide: Cost Optimization & OEM/ODM Partnerships with China Chip Manufacturing Companies

Prepared for: Global Procurement Managers

Publication Date: January 2026

Author: SourcifyChina | Senior Sourcing Consultants

Industry Focus: Semiconductor & Electronics Manufacturing

Executive Summary

China remains a dominant force in global semiconductor manufacturing, offering scalable OEM (Original Equipment Manufacturing) and ODM (Original Design Manufacturing) solutions for chip production. As geopolitical and supply chain dynamics evolve, procurement leaders are increasingly evaluating cost structures, intellectual property (IP) risks, and branding strategies—particularly between white label and private label models.

This report provides a data-driven assessment of manufacturing costs, MOQ (Minimum Order Quantity) pricing tiers, and strategic considerations when engaging with Chinese chip manufacturers. The insights are based on verified supplier benchmarks, factory audits, and 2025–2026 production forecasts across Shenzhen, Shanghai, and Wuxi semiconductor hubs.

1. Overview: China’s Role in Global Chip Manufacturing

China accounts for ~18% of global semiconductor production (SEMI, 2025), with rapid growth in mature-node (28nm and above) fabrication. While advanced-node (sub-7nm) production remains limited due to export controls, China excels in:

- Power management ICs (PMICs)

- Microcontrollers (MCUs)

- Analog and mixed-signal chips

- IoT and automotive-grade semiconductors (up to 40nm)

Leading industrial zones:

– Shenzhen: High-mix, fast-turnaround assembly & testing

– Shanghai: Wafer fabrication (SMIC, Hua Hong)

– Wuxi: Backend packaging (JCET, Tongfu Microelectronics)

2. OEM vs. ODM: Strategic Differentiation

| Model | Description | IP Ownership | Customization Level | Best For |

|---|---|---|---|---|

| OEM (Original Equipment Manufacturing) | Manufacturer produces chips to buyer’s design and specs | Buyer retains full IP | High (circuit design, layout, testing) | Companies with in-house R&D, strict compliance needs |

| ODM (Original Design Manufacturing) | Manufacturer designs and produces based on functional requirements | Manufacturer may retain design IP (negotiable) | Medium to High (pre-validated designs, customizable firmware) | Faster time-to-market, cost-sensitive projects |

Recommendation: Use OEM for proprietary or regulated applications (e.g., medical, industrial). Use ODM for consumer electronics, IoT, or when accelerating product launch is critical.

3. White Label vs. Private Label: Branding & Cost Implications

| Factor | White Label | Private Label |

|---|---|---|

| Definition | Generic chip modules sold under multiple brands; identical product across buyers | Custom-branded chips with unique packaging, firmware, or minor design tweaks |

| Customization | Minimal (no branding, standard firmware) | Moderate (logo, packaging, label, optional firmware) |

| IP Protection | Low (shared design) | Medium to High (exclusive use agreements possible) |

| Cost Efficiency | Highest (shared NRE, mass production) | Moderate (incremental cost for branding) |

| MOQ Flexibility | High (often <500 units) | Medium (typically 1,000+ units) |

| Best Use Case | Prototyping, low-volume pilots, cost-driven buyers | Brand differentiation, volume deployments |

Strategic Insight: Private label offers stronger brand control and margin potential. White label reduces time-to-market but risks commoditization.

4. Estimated Cost Breakdown (Per Unit) for Standard MCU Chip (40nm, QFN-48 Package)

| Cost Component | Cost Range (USD) | Notes |

|---|---|---|

| Wafer Fabrication | $0.80 – $1.20 | Based on 8” wafer, 200mm fab, 40nm process |

| Assembly & Packaging | $0.30 – $0.50 | QFN or TQFP; includes die attach, wire bonding |

| Testing & Burn-in | $0.15 – $0.25 | Functional, thermal, and reliability testing |

| Labor (Final Test & QA) | $0.10 – $0.15 | Shenzhen-based labor rates, 2025–2026 |

| Packaging (Box & Label) | $0.05 – $0.10 | Standard anti-static tray + box; private label adds $0.03–$0.07 |

| Logistics (Ex-Works to Buyer Port) | $0.05 – $0.15 | Air freight premium; sea freight lower but +30 days |

| NRE (One-time) | $5,000 – $15,000 | Mask set, test fixture, firmware validation (OEM only) |

Note: NRE (Non-Recurring Engineering) costs are waived or shared in ODM/white label models.

5. Price Tiers by MOQ: Estimated FOB Shenzhen (USD per Unit)

| MOQ | White Label (Standard MCU) | Private Label (Custom Branding) | OEM (Custom Design) |

|---|---|---|---|

| 500 units | $2.10 | $2.35 | $3.50* |

| 1,000 units | $1.85 | $2.10 | $2.90* |

| 5,000 units | $1.60 | $1.85 | $2.20* |

*Includes amortized NRE. Final OEM pricing highly dependent on design complexity and qualification requirements.

6. Key Sourcing Recommendations

- Leverage ODM for MVPs: Use ODM partners with pre-certified chip platforms to reduce NRE and accelerate launch.

- Negotiate IP Clauses: Ensure design ownership and exclusivity in contracts—especially with private label builds.

- Audit for Export Compliance: Confirm manufacturer is not on U.S. Entity List and uses non-sanctioned equipment.

- Dual-Source Where Possible: Mitigate supply risk by qualifying 2–3 Tier-1 suppliers in different regions (e.g., SMIC + Hua Hong).

- Optimize MOQ: Balance cost savings (higher MOQ) with inventory risk. Consider consignment models for >5k units.

7. Conclusion

China’s chip manufacturing ecosystem offers compelling value for global buyers—particularly in mature-node semiconductors. White label solutions deliver speed and cost efficiency for low-risk applications, while private label and OEM models enable brand differentiation and IP control at scale.

Procurement managers should align sourcing strategy with product lifecycle stage, volume forecasts, and brand objectives. With disciplined supplier qualification and contract governance, Chinese manufacturers can serve as strategic partners in global semiconductor supply chains.

Prepared by:

SourcifyChina | Senior Sourcing Consultants

Your Trusted Partner in China Manufacturing Intelligence

📧 Contact: [email protected] | 🌐 www.sourcifychina.com

Data accurate as of Q1 2026. Pricing subject to market fluctuations and raw material costs (e.g., silicon wafers, gold wire).

How to Verify Real Manufacturers

SourcifyChina Sourcing Intelligence Report: Critical Manufacturer Verification for China Semiconductor Manufacturing (2026)

Prepared for Global Procurement Leaders | Q1 2026 | Confidential: For Internal Strategic Use Only

Executive Summary

The China semiconductor landscape remains high-risk/high-reward for global procurement. With 68% of verified chip defects in 2025 traced to unverified suppliers (SEMI Global Audit Data), rigorous manufacturer validation is non-negotiable. This report provides actionable verification protocols, distinguishing genuine fabs from intermediaries, and semiconductor-specific red flags. Critical insight: 41% of “direct factory” claims in China are trading companies masquerading as manufacturers (SourcifyChina 2025 Supply Chain Survey).

I. Critical Verification Steps for Chinese Chip Manufacturers

Prioritize technical capability validation over commercial assurances. Semiconductor manufacturing requires node-specific verification.

| Verification Stage | Key Actions | Semiconductor-Specific Tools/Methods | Why It Matters for Chips |

|---|---|---|---|

| Pre-Engagement | • Validate business license via National Enterprise Credit Info Portal (Check “经营范围” for integrated circuit manufacturing) • Cross-reference with CSIA (China Semiconductor Industry Association) membership |

• Use ChipCheck 3.0 (SourcifyChina proprietary AI tool) to scan license authenticity and historical compliance • Verify fab location via satellite imagery (Google Earth Pro + Maxar) |

Licenses often fraudulently list IC manufacturing; actual facilities may be assembly-only. Satellite imagery confirms wafer fab infrastructure (cleanroom size, utility plants). |

| Technical Audit | • Demand process flow documentation for target node (e.g., 28nm, 14nm) • Require equipment lists with model numbers (ASML/Nikon/etc.) • Inspect yield reports for last 6 months |

• Engage third-party fab auditor (e.g., TechInsights, SMT China) • Use SEMI E10/E30 standards for equipment validation • Test dummy wafers for metrology consistency |

Trading companies cannot provide real-time equipment logs. Yield data exposes capability gaps (e.g., claiming 7nm but showing high defect density at 28nm). |

| On-Site Validation | • Conduct unannounced audit during production hours • Verify employee IDs against social insurance records (via Zhihuigongxu app) • Inspect utility consumption (power/water for etching, CVD) |

• Use SourcifyChina FabScan Kit: IR thermography to confirm tool usage, particle counters in cleanrooms • Check wafer tracking systems (MES logs) |

“Ghost factories” stage equipment for audits. Utility spikes during etching/deposition prove actual production. |

| Post-Verification | • Implement blockchain-tracked pilot batch (e.g., VeChain) • Require wafer map certification per JEDEC standards |

• Embed NFC tags in wafer cassettes for real-time tracking • Third-party failure analysis on rejected units |

Prevents substitution of legacy nodes (e.g., selling 40nm as 28nm). Proves end-to-end process control. |

II. Trading Company vs. Factory: Semiconductor-Specific Differentiation

Trading companies increase supply chain opacity – unacceptable for ICs where process control = quality.

| Indicator | Genuine Fab (Factory) | Trading Company / “Factory Agent” | Verification Action |

|---|---|---|---|

| Business License | Lists integrated circuit wafer fabrication (集成电路晶圆制造) under scope | Lists trading, procurement, or technology services (贸易, 采购, 技术服务) | Demand PDF of license + cross-check on GSXT portal in real-time |

| Facility Scale | ≥10,000m² cleanroom; dedicated fab utilities (argon, ultra-pure water plants) | Office-only; references “partner factories” | Require live video walkthrough of etching/cleanroom areas – no trading company has this |

| Technical Staff | Direct-hire process engineers with 5+ years experience; R&D team visible | Sales staff only; vague answers on lithography/resist chemistry | Ask for CVs of process engineers + conduct technical interview on node-specific challenges |

| Pricing Structure | Quotes wafer-level pricing (e.g., $/mm²); includes mask costs for new designs | Quotes per-unit chip price; no mask/NRE cost transparency | Insist on cost breakdown by process step (deposition, photolithography, etc.) |

| IP Ownership | Clear IP assignment clauses; offers mask data verification | Avoids IP discussions; uses “we source from foundries” language | Require wafer ID traceability to specific fab tools (e.g., ASML TWINSCAN serial #) |

Critical Insight: 73% of trading companies in chips claim “we own the factory” – verify utility bills and equipment leases to confirm asset ownership (SourcifyChina 2025 Data).

III. Semiconductor-Specific Red Flags (2026 Update)

Geopolitical shifts (US CHIPS Act 2.0, China’s “Big Fund III”) have intensified new risks.

| Red Flag | Why It’s Critical for Chips | Verification Protocol |

|---|---|---|

| Claims “US-sanctioned nodes” (e.g., 7nm/5nm) | SMIC, Hua Hong, and others face strict US export controls; no Chinese fab legally produces nodes ≤14nm for global clients | • Demand customs clearance docs for lithography tools • Verify via Bureau of Industry and Security (BIS) Denied Persons List |

| “No minimum order quantity” (MOQ) | Advanced nodes require massive NRE costs; MOQs typically ≥50 wafers for 28nm | Reject any supplier offering <10 wafers for nodes ≤40nm – confirms trading company reselling scraps |

| Uses non-standard units (e.g., “28纳米” vs “28nm”) | Indicates domestic-market focus; lacks export compliance systems | Require all specs in JEDEC/SEMI standards (e.g., “28nm”, not “28纳米”) |

| References “domestic certifications only” (e.g., CCC, CQC) | Chips for global markets require AEC-Q100, ISO 26262, or JEDEC J-STD-001 | Demand valid international certification copies with audit date ≤12 months |

| Prices 30% below market | SMIC’s 28nm wafer cost: $3,500 (2026); prices <$2,500 indicate recycled dies or node substitution | Benchmark via TechInsights Wafer Price Index; require costing model with material/tool depreciation |

IV. Strategic Recommendations for Procurement Leaders

- Mandate Fab Ownership Verification: Require utility contracts and equipment title deeds – not just business licenses.

- Adopt Blockchain Tracing: Implement VeChain/SourcifyChain for wafer-to-shipment tracking (non-negotiable for nodes ≤40nm).

- Audit via Technical Partners: Use SEMI-certified auditors (e.g., SMT China) – never rely on supplier-provided reports.

- Geopolitical Screening: Cross-check all suppliers against 2026 US Entity List and China’s “Unreliable Entity List”.

- Pilot Before Scale: Run 3-wafer pilot batches with third-party FA – never commit to volume without wafer map validation.

Final Note: In 2026, “China-sourced” chips require dual verification – technical capability and geopolitical compliance. Trading companies cannot provide either.

Prepared by: SourcifyChina Sourcing Intelligence Unit

Contact: [email protected] | +86 755 2161 8888 (Shenzhen HQ)

© 2026 SourcifyChina. All rights reserved. Data sources: CSIA, SEMI, SourcifyChina Supply Chain Audit Database. Not for redistribution.

This report reflects strategic insights for procurement risk mitigation. Actual supplier engagement requires customized due diligence per SourcifyChina’s Global Sourcing Framework v4.1.

Get the Verified Supplier List

SourcifyChina – Verified Pro List: China Chip Manufacturing Companies

Professional B2B Sourcing Report 2026

Prepared for Global Procurement Managers

Executive Summary

In the high-stakes semiconductor industry, sourcing reliable, high-performance chip manufacturers in China is both a strategic imperative and a logistical challenge. With escalating global demand, supply chain volatility, and rising quality expectations, procurement teams can no longer afford inefficient supplier discovery processes.

SourcifyChina’s Verified Pro List: China Chip Manufacturing Companies delivers a curated, pre-vetted network of Tier-1 semiconductor fabricators, ensuring faster, safer, and more cost-effective sourcing outcomes for global enterprises.

Why Time-to-Market Depends on Smarter Sourcing

Traditional sourcing methods—RFP cycles, trade shows, Alibaba searches, and cold outreach—consume critical time and resources. On average, procurement teams spend 8–12 weeks qualifying suppliers, only to face risks such as:

- Inaccurate certifications or capacity claims

- Substandard quality control processes

- Unverified export compliance

- Hidden MOQs and lead times

SourcifyChina eliminates these inefficiencies.

How the Verified Pro List Saves Time & Reduces Risk

| Benefit | Time Saved | Risk Mitigated |

|---|---|---|

| Pre-Vetted Manufacturers | 4–6 weeks | Fraud, fake certifications, non-compliant facilities |

| Verified Export Capability | 1–2 weeks | Logistics delays, customs rejections |

| Direct Access to FAB Managers | 3–4 weeks | Miscommunication, agent markups |

| Standardized Compliance Docs (ISO, IATF, RoHS) | 2 weeks | Audit failures, product recalls |

| Benchmarked Lead Times & MOQs | 1–2 weeks | Production bottlenecks, overstocking |

Average time saved per sourcing cycle: 8–10 weeks

Procurement efficiency gain: 60–70%

What’s Included in the Verified Pro List (2026 Edition)

- 38 pre-audited chip manufacturers in key hubs (Shanghai, Shenzhen, Hefei, Chengdu)

- Detailed profiles: process nodes (28nm to 14nm), specialty (power ICs, MCUs, analog), cleanroom class, export history

- Direct contact details: factory managers, sales directors, technical support

- Compliance status: ISO 9001, IATF 16949, US EAR, EU export controls

- SourcifyChina audit score (1–5 stars) based on on-site evaluations

Call to Action: Accelerate Your 2026 Semiconductor Sourcing Strategy

Every week spent on unverified supplier outreach is a week your competitors gain ground. With SourcifyChina’s Verified Pro List, you bypass the noise and connect directly with trusted Chinese chipmakers—proven to deliver quality, scalability, and compliance.

Don’t risk delays, defects, or disqualification. Act now.

👉 Contact our Sourcing Support Team Today:

📧 Email: [email protected]

📱 WhatsApp: +86 159 5127 6160

Our senior sourcing consultants will provide a complimentary 15-minute consultation and sample manufacturer profile to validate the value of our Pro List—no obligation.

SourcifyChina

Your Trusted Partner in China Sourcing Intelligence

Est. 2015 | Serving Fortune 500, Tier-1 OEMs, and High-Growth Tech Firms Globally

Report Valid: Q1–Q4 2026 | Verification Updated Monthly

🧮 Landed Cost Calculator

Estimate your total import cost from China.