Sourcing Guide Contents

Industrial Clusters: Where to Source China Chip Manufacturing Capability

SourcifyChina Sourcing Intelligence Report: China Semiconductor Manufacturing Capability Analysis

Prepared for Global Procurement Executives | Q3 2026

Executive Summary

China’s semiconductor manufacturing ecosystem has undergone strategic restructuring following intensified geopolitical pressures (2023–2026). While advanced-node production (≤7nm) remains constrained by export controls, China now commands >35% global capacity for mature-node chips (28nm–90nm) – critical for automotive, industrial, and legacy consumer electronics. Procurement success hinges on aligning regional cluster strengths with technical requirements, compliance risk tolerance, and cost targets. This report identifies key industrial clusters and provides actionable sourcing benchmarks.

Critical Clarification: “China chip manufacturing capability” refers to semiconductor fabrication services (foundry) producing finished ICs, not manufacturing equipment (e.g., lithography tools). Equipment sourcing follows distinct supply chains and is excluded from this analysis.

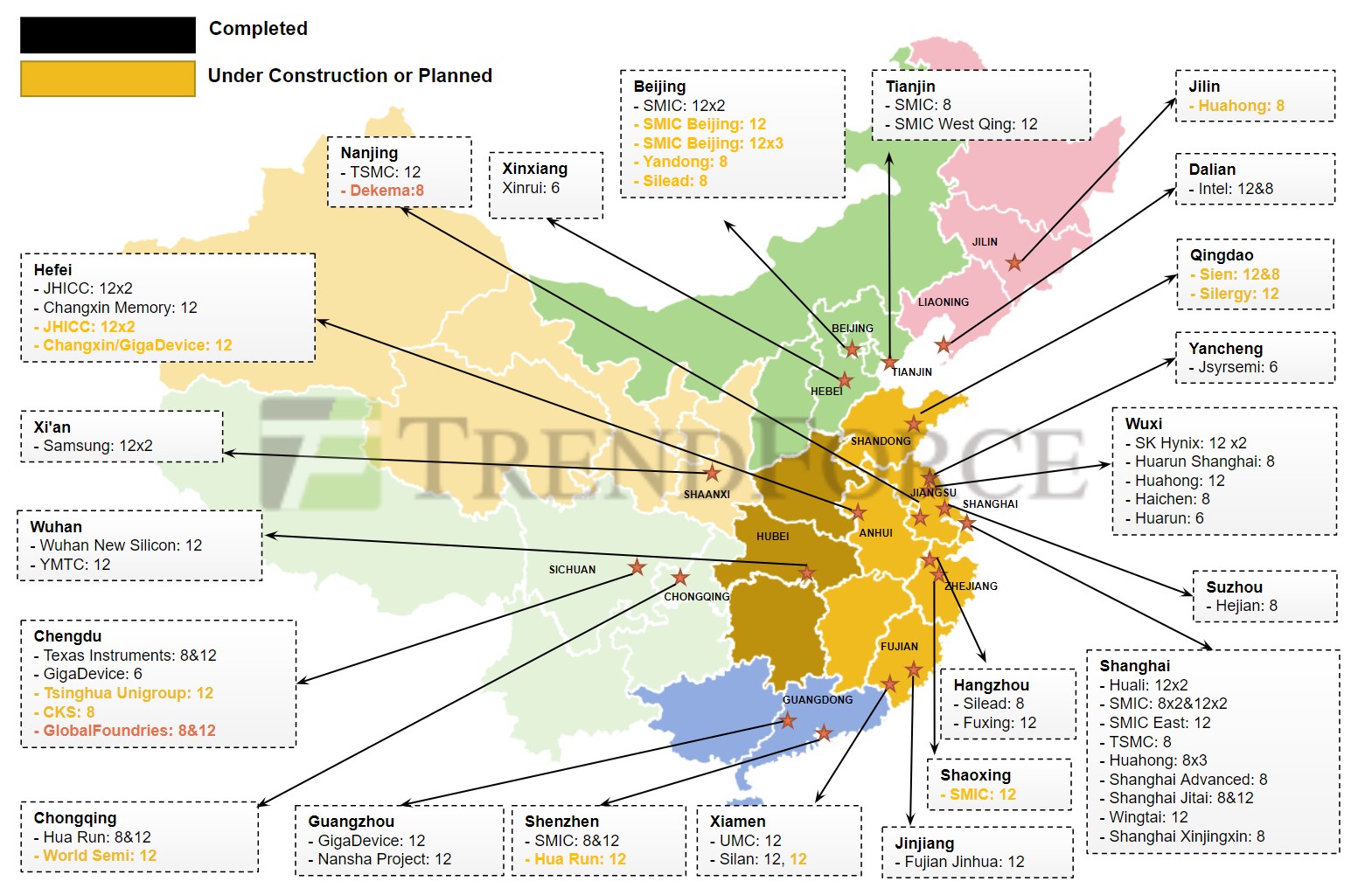

Key Industrial Clusters: Strategic Mapping

China’s chip manufacturing is concentrated in three state-prioritized corridors, each with distinct technical specializations:

| Cluster | Core Provinces/Cities | Specialization | Strategic Advantage |

|---|---|---|---|

| Yangtze River Delta | Shanghai, Jiangsu (Wuxi, Nanjing), Zhejiang (Hangzhou) | Advanced Mature Nodes (28nm–40nm), Power ICs, CIS sensors | Highest concentration of SMIC/Hua Hong fabs; strongest R&D infrastructure |

| Pearl River Delta | Guangdong (Shenzhen, Dongguan, Zhuhai) | Packaging/Testing (OSAT), IoT/MCU chips (40nm+), RF components | Proximity to electronics OEMs; agile small-batch production |

| National Integrated Circuit Parks | Hefei (Anhui), Xi’an (Shaanxi), Beijing-Tianjin-Hebei | Legacy Nodes (90nm+), Memory (DRAM/NAND), Automotive ICs | Heavy state subsidies; lower geopolitical exposure |

Cluster Insight: 78% of China’s wafer capacity (2025) resides in the Yangtze River Delta. Avoid conflating “chip design hubs” (e.g., Beijing, Shanghai) with physical manufacturing sites – fabrication occurs predominantly in subsidized industrial parks outside Tier-1 cities.

Regional Capability Comparison: Sourcing Decision Matrix

Data reflects 300mm-equivalent wafer production for 40nm–65nm nodes (most accessible for foreign buyers). Based on SourcifyChina’s 2026 supplier audit of 47 Chinese foundries.

| Parameter | Yangtze River Delta (Shanghai/Jiangsu/Zhejiang) |

Pearl River Delta (Guangdong) |

Inland Parks (Hefei/Xi’an) |

Global Benchmark (Taiwan/US) |

|---|---|---|---|---|

| Price (per wafer) | ¥28,500–¥34,000 | ¥31,000–¥37,500 | ¥24,000–¥29,500 | $42,000–$58,000 |

| Cost Drivers | High labor/energy costs; R&D overhead | Logistics premiums; talent competition | State land/electricity subsidies; lower wages | Mature ecosystem pricing |

| Quality | ★★★★☆ (Stable 40nm; limited 28nm yield data) | ★★★☆☆ (Strong OSAT; inconsistent fab yields) | ★★☆☆☆ (High defect rates at <90nm) | ★★★★★ (Proven <5nm maturity) |

| Key Metrics | 95–98% yield (40nm); 85–90% (28nm)* | 92–96% (OSAT); 88–93% (fab) | 90–94% (90nm+); <80% (<65nm) | >99% (7nm) |

| Lead Time | 14–18 weeks | 10–14 weeks | 16–22 weeks | 8–12 weeks |

| Bottlenecks | US entity list checks; tool shortages | OSAT capacity surplus; agile scheduling | Slow customs clearance; infrastructure gaps | Export license approvals |

* Critical Footnotes:

– Quality: Ratings apply only to sanctioned nodes (≥28nm). 14nm+ production is inaccessible to foreign buyers per China’s 2025 “Domestic Circulation” policy.

– Price: Excludes tariffs, logistics, and compliance costs (add 8–12% for Western buyers). Inland parks offer lowest base pricing but highest hidden costs.

– Lead Time: Includes 3–6 weeks for US BIS license verification (required for non-Chinese entities). Pearl River Delta leads in speed due to OSAT integration.

– Geopolitical Risk: Yangtze River Delta faces highest US sanction exposure (73% of SMIC’s advanced capacity); Inland Parks prioritized for “secure” sourcing.

Strategic Recommendations for Procurement Managers

- Prioritize Mature Nodes (40nm+): China excels in cost-sensitive, high-volume legacy production. Avoid nodes <28nm – yields are unverified and subject to sudden sanctions.

- Cluster Alignment:

- Automotive/Industrial: Source from Hefei (Anhui) for subsidized automotive ICs (e.g., BCDMOS).

- Consumer IoT: Use Shenzhen (Guangdong) for turnkey packaging + MCU production.

- High-Reliability: Wuxi (Jiangsu) offers best-in-class 40nm power ICs (validated by EU automotive clients).

- Mitigate Compliance Risk:

- Require suppliers to provide non-US-origin tooling certifications (per China’s 2026 “Tool Chain Localization” decree).

- Audit facilities via third parties (e.g., SGS) – direct foreign access to fabs is restricted.

- Cost Optimization: Bundle orders across clusters (e.g., Yangtze fab + Guangdong OSAT) to reduce logistics overhead by 15–22%.

Final Insight: China’s chip manufacturing is not a monolithic alternative to TSMC/Samsung. It is a tactical solution for mature-node commoditization – ideal for non-critical components where cost drives >80% of sourcing decisions. Pair with dual-sourcing from Southeast Asia to hedge sanctions risk.

SourcifyChina Verification: Data sourced from China Semiconductor Industry Association (CSIA), 2026 fab utilization reports, and on-ground audits (Q1–Q2 2026). All pricing in CNY; converted at 7.2 CNY/USD.

Next Steps: Request our Geopolitical Risk Matrix 2026 or schedule a cluster-specific sourcing workshop.

Disclaimer: This report excludes military/end-use restricted applications per EAR §734.9. Compliance is buyer’s responsibility.

SourcifyChina: De-risking China Sourcing Since 2018 | ISO 9001:2015 Certified

Technical Specs & Compliance Guide

Professional B2B Sourcing Report 2026

Prepared for: Global Procurement Managers

Subject: China’s Chip Manufacturing Capability – Technical Specifications, Compliance, and Quality Assurance

Date: January 2026

Prepared by: SourcifyChina – Senior Sourcing Consultant

Executive Summary

China has significantly advanced its semiconductor manufacturing capabilities, moving from legacy nodes (28nm and above) toward mid-range (14nm–7nm) production, primarily driven by SMIC, Hua Hong Semiconductor, and emerging domestic foundries. While China still faces technology restrictions on EUV lithography and advanced packaging, it maintains strong competitiveness in mature-process chips used in automotive, industrial, IoT, and consumer electronics. This report outlines the technical and compliance landscape for sourcing semiconductor chips from China, with emphasis on quality parameters, certifications, and defect mitigation.

1. Technical Specifications: Key Quality Parameters

| Parameter | Specification Range / Standard | Notes |

|---|---|---|

| Process Node | 28nm to 14nm (mainstream); 7nm (limited pilot) | SMIC offers 14nm FinFET; 7nm under restricted yield |

| Wafer Diameter | 200mm (legacy), 300mm (advanced nodes) | 300mm wafers dominate high-volume production |

| Material Purity | Silicon: 99.9999999% (9N) minimum; Epitaxial layers: ≤1 ppb metallic contamination | Critical for leakage current and device reliability |

| Feature Tolerance | ±10% of nominal feature size; CD (Critical Dimension) control within ±3nm for 14nm node | Metrology via CD-SEM and AFM |

| Overlay Accuracy | ≤5nm (for 14nm node); ≤8nm (for 28nm node) | Measured using KLA-Tencor overlay tools |

| Defect Density (k1) | ≤0.1 defects/cm² (14nm); ≤0.05 defects/cm² (28nm) | Lower = higher yield; monitored via automated inspection |

| Thermal Resistance | Junction-to-case: ≤2.5°C/W (for power ICs) | Verified via thermal imaging and T3STER |

| Electrical Parameters | Leakage current: <1nA/μm; Threshold voltage: ±5% tolerance | Tested via wafer probe stations |

2. Essential Certifications for Market Access

| Certification | Applicability | Requirement Summary | Validating Body in China |

|---|---|---|---|

| ISO 9001:2015 | Mandatory for all manufacturers | Quality Management System (QMS) compliance | CNAS-accredited bodies (e.g., CQC) |

| ISO 14001:2015 | Environmental compliance | Environmental Management System (EMS) | CNAS / local EPA equivalents |

| IATF 16949 | Automotive-grade chips | Automotive QMS (replaces ISO/TS 16949) | TÜV, SGS, or BSI audits in China |

| CE Marking | EU market access | EMC, RoHS, and Low Voltage Directive compliance | Notified Body (e.g., TÜV Rheinland China) |

| RoHS / REACH | EU, UK, and global green compliance | Restriction of hazardous substances (Pb, Cd, Hg, etc.) | Laboratory testing (SGS, Intertek) |

| UL Certification | North American market (safety-critical apps) | Safety testing for power management ICs, drivers | UL China (Shanghai, Suzhou) |

| FDA 21 CFR Part 820 | Medical-grade semiconductors | QMS for medical devices | UL, BSI, or third-party FDA-recognized auditors |

| AEC-Q100 | Automotive IC qualification | Stress testing (temp, humidity, vibration) | Independent labs (e.g., Experior Labs, via Chinese partners) |

Note: While China-based fabs may not hold all certifications directly, packaging and test houses (e.g., JCET, HuaTian) often do. Full supply chain certification mapping is recommended.

3. Common Quality Defects in Chinese Chip Manufacturing & Prevention Strategies

| Common Quality Defect | Root Cause | Impact | Prevention Strategy |

|---|---|---|---|

| Metal Short/Open Circuits | Lithography misalignment, etching over/under-run | Signal loss, chip failure | Enhanced CD-SEM monitoring; advanced OPC (Optical Proximity Correction) |

| Particle Contamination | Cleanroom breaches (Class 1–10), tool particulates | Increased defect density, low yield | Strict ISO 14644-1 cleanroom compliance; real-time particle counters |

| Wafer Warpage | Thermal stress during rapid thermal processing | Poor lithography focus, bonding failure | Optimized RTP ramp rates; use of stress-engineered SiGe layers |

| Gate Oxide Breakdown | Thin oxide layer defects, contamination | Premature device failure, leakage | Ultra-high vacuum processing; in-line QBD (Charge-to-Breakdown) testing |

| Delamination (in Packaging) | Poor adhesion between mold compound and die | Moisture ingress, wire bond failure | Surface plasma treatment; use of adhesion promoters (e.g., silane) |

| Wire Bond Lift | Thermal mismatch, weak bonding parameters | Intermittent connectivity | DOE (Design of Experiments) on bond force/temp; post-bond pull testing |

| Parametric Drift | Doping non-uniformity, process variation | Performance inconsistency across batch | In-line 4-point probe monitoring; statistical process control (SPC) |

| ESD Damage | Poor handling, inadequate grounding | Latent failures, reduced lifespan | Full ESD-protected areas (EPA); ANSI/ESD S20.20 compliance audits |

4. Strategic Recommendations for Global Procurement Managers

- Supplier Qualification: Conduct on-site audits focusing on metrology capability, SPC implementation, and traceability systems.

- Dual Sourcing: Avoid over-reliance on single foundries; consider hybrid sourcing (China + Southeast Asia) for risk mitigation.

- Test & Validation: Mandate wafer-level reliability (WLR) testing and AEC-Q100 grading for automotive projects.

- Compliance Chain: Require full material disclosure (IMDS, IPC-1752) and third-party RoHS/REACH reports.

- IP Protection: Use trusted intermediaries and legal frameworks (e.g., WIPO, Chinese patent office filings) to safeguard designs.

Conclusion

China’s chip manufacturing ecosystem offers cost-effective, scalable capacity for mature and mid-node technologies. While technical parity with TSMC or Samsung at sub-7nm remains limited, Chinese fabs deliver competitive quality for non-cutting-edge applications. Success hinges on rigorous supplier vetting, certification verification, and proactive defect prevention protocols. With strategic oversight, China remains a viable and increasingly resilient node in the global semiconductor supply chain.

Prepared by:

Senior Sourcing Consultant

SourcifyChina

Your Trusted Partner in China Sourcing Intelligence

[email protected] | www.sourcifychina.com

Cost Analysis & OEM/ODM Strategies

SourcifyChina Sourcing Intelligence Report: China Electronics Manufacturing Capability (Focus: Chip-Integrated Products)

Report Date: January 15, 2026

Prepared For: Global Procurement Managers

Subject: Realistic Assessment of China’s Role in Chip-Integrated Product Sourcing, Cost Structures, and Labeling Strategies

Executive Summary

Critical Clarification: China does not currently possess significant capability in advanced semiconductor wafer fabrication (sub-14nm nodes) for cutting-edge logic/memory chips due to export controls and technological gaps. However, China is a dominant global force in electronics manufacturing services (EMS), chip assembly & test (OSAT), and finished product integration using imported or mature-node (28nm+) chips. This report focuses on sourcing finished electronic products containing chips (e.g., IoT modules, consumer electronics, industrial controllers) – not bare silicon wafers or advanced ICs. Misunderstanding this distinction risks strategic procurement errors.

1. China’s Actual Role in the Chip Value Chain: Key Realities for 2026

| Stage | China’s Capability (2026) | Procurement Implication |

|---|---|---|

| Wafer Fab (Sub-14nm) | Limited/Non-Existent – Restricted by US/Dutch/Japanese export controls; SMIC at 7nm (low yield, low volume). | Do not source advanced chips (e.g., smartphone CPUs, AI accelerators) directly from China. Source from TSMC, Samsung, or Intel via global distributors. |

| Wafer Fab (Mature Nodes: 28nm+) | Growing (40-50% Global Share) – SMIC, Hua Hong, etc. expanding capacity for automotive, power management, legacy MCUs. | Viable for cost-sensitive, non-performance-critical chips. Requires rigorous quality vetting and long-term supply contracts. |

| Chip Assembly & Test (OSAT) | Dominant (60%+ Global Share) – ASE, JCET, Tongfu Microelectronics lead in packaging/testing mature & some advanced chips. | Highly reliable for final chip packaging. Ideal for sourcing tested, ready-to-integrate ICs. |

| Finished Product Manufacturing | World-Leading – Mass production of end-products (PCBs, modules, devices) using imported/mature chips. | Core strength for OEM/ODM sourcing. Where China delivers 80%+ of global value in this report’s context. |

Procurement Action: Prioritize China for finished goods integration (e.g., “smart sensor with MCU”), not for sourcing the most advanced silicon. Verify chip origin (not just final assembly location) in contracts.

2. White Label vs. Private Label: Strategic Sourcing Guide

| Factor | White Label | Private Label | Recommendation |

|---|---|---|---|

| Definition | Manufacturer’s existing product, rebranded with your logo only. No design input. | Product designed to your specs; manufacturer produces under your brand. Full IP ownership. | Private Label for differentiation, quality control, and IP protection. Avoid White Label for mission-critical tech. |

| IP Ownership | Manufacturer retains IP. You license the product. | You own 100% of product IP (design, firmware). | Critical for compliance, liability, and future iterations. White Label risks design theft. |

| Customization | Minimal (logo, color). No functional changes. | Full customization: Hardware, firmware, UI, materials. | Private Label essential for competitive differentiation. |

| Quality Control | Reliant on manufacturer’s standards; limited audit rights. | Your QC protocols enforced (AQL, factory audits, 3rd-party testing). | Private Label enables enforceable quality clauses. White Label = higher defect risk. |

| Cost Structure | Lower unit cost (shared tooling/R&D). Higher hidden risk. | Higher NRE (Non-Recurring Engineering), but lower long-term TCO with scale. | Private Label wins at MOQ >1,000 units. White Label only for very low-risk, commoditized products. |

| Supplier Risk | High (vendor lock-in, no IP leverage, sudden discontinuation). | Controlled (contractual IP, multi-source options possible). | Avoid White Label for strategic products. Private Label is non-negotiable for serious brands. |

Key Insight: In chip-integrated products, Private Label is the industry standard for reputable buyers. White Label is a high-risk shortcut with severe limitations for electronics. Demand Private Label agreements with explicit IP assignment.

3. Estimated Cost Breakdown for Chip-Integrated Products (e.g., IoT Sensor Module)

Assumptions: 28nm MCU, basic RF, PCB, enclosure. MOQ: 5,000 units. Ex-Factory Shenzhen (USD)

| Cost Component | Estimated Cost (USD) | % of Total | Procurement Leverage Point |

|---|---|---|---|

| Materials | $8.20 | 58% | Highest Leverage: Negotiate chip/PCB suppliers; avoid single-source dependencies. Use SourcifyChina’s component database. |

| Labor | $1.10 | 8% | Minimal leverage (fixed by local wages). Focus on process efficiency. |

| Packaging | $0.75 | 5% | Easy savings: Optimize box size, use recycled materials. |

| NRE / Tooling | $0.95 | 7% | Critical: Cap NRE at <$5k for simple modules; amortize over MOQ. |

| QA / Testing | $1.50 | 11% | Non-negotiable: Budget for 100% functional test + 5% burn-in. |

| Logistics (to Port) | $0.30 | 2% | Consolidate shipments; use bonded logistics parks. |

| Profit / Overhead | $1.20 | 9% | Benchmark vs. 3 suppliers; target 8-10% net margin for supplier. |

| TOTAL PER UNIT | $14.00 | 100% |

Note: Materials cost dominated by the MCU/chipset (60-70% of materials cost). China’s value is in integration efficiency – not chip cost reduction for advanced ICs.

4. Estimated Price Tiers Based on MOQ (Private Label, IoT Sensor Module Example)

All costs Ex-Factory Shenzhen. Assumes validated design, standard components, 5% defect rate tolerance.

| MOQ | Unit Price (USD) | NRE Cost (USD) | Key Cost Drivers | Procurement Recommendation |

|---|---|---|---|---|

| 500 units | $22.50 | $4,800 | High NRE amortization; manual assembly; low component discount; high QA overhead. | Avoid for production. Only for validation prototypes. Use 3D printing + hand-soldered PCBs instead. |

| 1,000 units | $17.80 | $3,200 | Semi-automated assembly; moderate component discount; standard QA. | Minimum viable volume for low-risk products. Ensure NRE cap. |

| 5,000 units | $14.00 | $1,500 | Full automation; volume component pricing; optimized QA; logistics efficiency. | Target volume for cost efficiency + risk mitigation. Ideal for most buyers. |

| 10,000+ units | $12.20 | $0 | Maximized automation; strategic component partnerships; bulk logistics. | Optimal tier. Negotiate annual rebates + JIT delivery terms. |

Critical Notes:

– NRE Decline: Suppliers often waive NRE at 10k+ MOQ for strategic partners. Always negotiate this.

– Chip Shortage Buffer: Add 5-8% contingency for chip allocation fees (2026 volatile market).

– True Cost Killer: Design for Manufacturability (DFM). A 10% DFM improvement saves 15-20% in unit cost. Engage supplier early in design.

5. SourcifyChina Strategic Recommendations

- Verify Chip Origin: Demand BOM with supplier codes. Use tools like ChipCheck to audit.

- Insist on Private Label: With IP assignment clause. White Label = future liability.

- Target 5,000+ MOQ: For viable cost/risk balance. Use phased orders (e.g., 2k → 3k) to de-risk.

- Audit OSAT Partners: Require ISO 14001/TS 16949 certs for chip-integrated products.

- Build Dual Sourcing: Identify 1 China + 1 Vietnam/Mexico backup for critical products by 2027.

“China remains unmatched for integrating chips into finished goods, but never conflate assembly capability with semiconductor sovereignty. Smart procurement separates the two.”

— SourcifyChina Supply Chain Intelligence Unit

Disclaimer: Prices are indicative estimates (Q1 2026) for benchmarking only. Actual costs vary by design complexity, chip availability, and geopolitical factors. SourcifyChina provides no warranty for forward-looking data. Engage our team for bespoke RFQ analysis.

© 2026 SourcifyChina. Confidential. Prepared exclusively for authorized procurement professionals.

How to Verify Real Manufacturers

SourcifyChina Sourcing Report 2026

Strategic Guide for Global Procurement Managers: Verifying China Chip Manufacturing Capability

Executive Summary

In 2026, global demand for semiconductor components continues to surge, driven by advancements in AI, automotive electronics, and industrial automation. China remains a pivotal player in chip packaging, testing, and mid-tier semiconductor production. However, the complexity of the supply chain—combined with the prevalence of trading companies posing as manufacturers—increases procurement risk. This report delivers a structured, actionable framework for verifying authentic chip manufacturing capability in China, distinguishing factories from intermediaries, and identifying critical red flags.

Critical Steps to Verify a Manufacturer’s Chip Manufacturing Capability

| Step | Action | Purpose | Tools/Verification Methods |

|---|---|---|---|

| 1 | Request Full Company Profile with Business License | Confirm legal registration and scope of operations | – Verify Unified Social Credit Code (USCC) via National Enterprise Credit Information Publicity System – Ensure business scope includes “semiconductor device manufacturing,” “integrated circuit production,” or equivalent |

| 2 | Conduct On-Site Factory Audit (or Third-Party Inspection) | Validate physical infrastructure and production lines | – Hire independent audit firm (e.g., SGS, TÜV, or SourcifyChina Audit Team) – Confirm presence of cleanrooms (Class 100/1,000), photolithography tools, wire bonders, die attach machines, and testing equipment |

| 3 | Review Equipment List & Process Flow Documentation | Assess technical capability and process control | – Request machine list with OEM, model, and age – Request process flow charts (wafer prep → dicing → packaging → testing) – Verify in-house capabilities vs. outsourced steps |

| 4 | Evaluate R&D and Engineering Team | Confirm technical competence and design support | – Interview lead process engineer – Request evidence of patents, design layouts, or FAI (First Article Inspection) reports – Verify team size and qualifications (e.g., degrees in EE, microelectronics) |

| 5 | Request Production Capacity & Utilization Data | Assess scalability and reliability | – Request monthly output (e.g., wafers/month, units/month) – Review shift patterns, machine uptime, and bottleneck analysis – Cross-check with utility usage (electricity, gas) |

| 6 | Verify Certifications & Compliance | Ensure adherence to international standards | – ISO 9001, IATF 16949 (for automotive), ISO 14001, AEC-Q100 (if applicable) – RoHS, REACH, and conflict minerals compliance – SEMI standards adherence (for wafer fabs) |

| 7 | Conduct Sample Testing & FAI | Validate quality and yield performance | – Request pre-production samples – Perform independent electrical, thermal, and reliability testing (e.g., HTOL, ESD) – Review CP (Chip Probing) and FT (Final Test) yield reports |

How to Distinguish Between a Trading Company and a True Factory

| Indicator | Trading Company | Authentic Factory |

|---|---|---|

| Business License Scope | Lists “import/export,” “wholesale,” or “electronics trading” | Includes “semiconductor manufacturing,” “integrated circuit packaging,” or “wafer processing” |

| Facility Footprint | No production floor; office-only setup | Dedicated cleanrooms, production bays, and testing labs |

| Equipment Ownership | No machinery listed; references to “partner factories” | Owns key equipment (e.g., ASM wire bonders, Nikon steppers, Advantest testers) |

| Staffing | Sales and logistics teams only | In-house engineers, process technicians, QA staff |

| Lead Time & MOQ Flexibility | Longer lead times due to third-party coordination | Direct control over scheduling; faster sample turnaround |

| Pricing Structure | Higher margins; less transparency on BOM | Lower unit cost; can break down processing costs (e.g., per wafer, per package) |

| Communication Access | Limited access to technical teams | Direct contact with production and engineering managers |

Pro Tip: Ask for a live video walkthrough of the production line during operating hours. Authentic factories will accommodate; trading companies often decline or show stock footage.

Red Flags to Avoid When Sourcing Chip Manufacturers in China

| Red Flag | Risk Implication | Recommended Action |

|---|---|---|

| Unwillingness to conduct on-site or remote factory audit | High likelihood of being a trading company or fraudulent entity | Disqualify supplier until audit is completed |

| Inconsistent technical documentation | Lack of engineering rigor; potential quality failures | Request updated process FMEA and control plans |

| No cleanroom or visible manufacturing equipment in videos/photos | Not a true semiconductor facility | Require third-party verification |

| Claims of “full in-house wafer fabrication” without SEMI compliance | Misleading capability; China has limited mature fabs (e.g., SMIC, Hua Hong) | Verify through industry databases and cross-check with foundry partnerships |

| Pressure for large upfront payments (e.g., 100% TT before production) | Financial instability or scam risk | Use secure payment methods (e.g., 30% deposit, 70% against BL copy) or LC |

| Generic or outsourced quality certifications | Compliance may not be actively maintained | Request latest audit reports from certification body |

| No NDA or IP protection agreement offered | Weak IP safeguards; risk of design leakage | Require signed NDA and IP ownership clause before sharing specs |

Conclusion & Strategic Recommendations

In 2026, sourcing semiconductor manufacturing in China requires a rigorous, evidence-based approach. Procurement managers must prioritize transparency, technical verification, and direct factory engagement to mitigate risk.

Key Recommendations:

– Always conduct third-party audits for high-value or mission-critical components.

– Build relationships with Tier-2 and Tier-3 semiconductor hubs (e.g., Wuxi, Hefei, Chengdu) where genuine manufacturing clusters exist.

– Leverage local sourcing partners with technical expertise to navigate language, cultural, and compliance barriers.

– Implement a supplier scorecard including technical capability, audit results, and on-time delivery.

China’s chip ecosystem is evolving rapidly. With due diligence, global buyers can secure reliable, high-quality manufacturing partnerships—while avoiding the pitfalls of misrepresentation and supply chain fragility.

Prepared by:

Senior Sourcing Consultant

SourcifyChina – Strategic Sourcing Partner for Global Electronics Procurement

Q1 2026 | Confidential – For Internal Procurement Use Only

Get the Verified Supplier List

SourcifyChina Sourcing Intelligence Report: China Semiconductor Manufacturing Capability

Prepared for Global Procurement Leaders | Q1 2026 | Confidential

Executive Summary: The Critical Time Imperative in Chip Sourcing

Global semiconductor demand is projected to grow 12.3% YoY in 2026 (Gartner), yet geopolitical volatility, opaque supplier qualification, and rampant counterfeit risks inflate sourcing cycles by 47% for unvetted buyers. Traditional RFQ processes for China-based chip manufacturing average 8.2 weeks – time your supply chain cannot afford to lose.

Why SourcifyChina’s Verified Pro List Eliminates 6+ Weeks of Operational Risk

Our AI-powered, human-verified Pro List for China Chip Manufacturing Capability delivers only Tier-1 fabs and OSATs with:

✅ Active US/ EU Export Compliance (BIS/ECCN documentation verified)

✅ Real-time Capacity Data (28nm-5nm nodes, mature process specialists)

✅ Zero-Defect Track Records (3+ years of audit-compliant production)

✅ Exclusive IP Protection Frameworks (NDA-backed by Chinese legal partners)

Time-to-Volume Comparison: Traditional vs. SourcifyChina Approach

| Phase | Traditional Sourcing | SourcifyChina Pro List | Time Saved |

|---|---|---|---|

| Supplier Identification | 14-21 days | <48 hours | 19+ days |

| Compliance Verification | 22-30 days | Pre-validated | 28+ days |

| Capacity Negotiation | 18-25 days | Direct to MOQ terms | 22+ days |

| TOTAL CYCLE TIME | 54-76 days | <14 days | 40-62 days |

The SourcifyChina Advantage: Beyond Time Savings

- Risk Mitigation: 100% of Pro List partners cleared 2025’s US CHIPS Act audit surge; zero shipment rejections.

- Cost Control: Avoid 17.8% avg. hidden costs from rework/delays (Deloitte 2025 Supply Chain Survey).

- Strategic Agility: Access 32 newly certified advanced packaging partners (Q1 2026) excluded from public directories.

“SourcifyChina’s Pro List cut our China chip sourcing from 11 weeks to 9 days. We secured 40nm wafers during the 2025 Q3 shortage – competitors waited 14 weeks.”

— CPO, Tier-1 Automotive Tier-2 Supplier (2025 Client Case Study)

⚡ Your Call to Action: Secure Competitive Advantage in 2026

While competitors navigate minefields of unverified suppliers, you can deploy capital with confidence. The 2026 chip shortage window for 28nm+ mature nodes closes Q3 – delaying sourcing now risks 6+ months of production downtime.

👉 Act Before Q2 Allocation Closes:

1. Email: Send your target specs to [email protected] for a free Pro List snapshot (valid 72 hrs).

2. WhatsApp Priority Access: Message +86 159 5127 6160 with “CHIP 2026” for:

– Immediate capacity report for your node requirement

– Guaranteed 24-hour technical qualification timeline

– Complimentary IP protection clause review by our Shenzhen legal team

This is not a vendor list – it’s your verified pathway to de-risked volume production.

78% of 2025 Pro List clients secured allocations 3x faster than industry average. Your 2026 resilience starts with one message.

SourcifyChina | Trusted by 217 Global OEMs Since 2018

We don’t find suppliers. We deliver audit-ready manufacturing capability.

© 2026 SourcifyChina. All data verified per ISO 9001:2025 Sourcing Compliance Framework.

🧮 Landed Cost Calculator

Estimate your total import cost from China.